우리는 16비트 컴퓨터를 설계하고 있다.

이전 포스팅([컴퓨터구조] 16비트 컴퓨터 설계하기 - Control unit 설계)에서는 Control unit을 공부했는데 여기서 timeT0, T1, ...의 발생을 보았고, 특히 fetch와 decode가 되는 time을 간접적으로 확인했다.

이렇게 명령이 수행되어져가는 time은 instruction cycle 개념과 관련이 있다고 이야기했다.

그래서 이번 포스팅에서는 instruction cycle을 공부할 것이다.

instruction cycle

▽ 메모리로부터 instruction을 fetch

▽ instruction을 decode

▽ 메모리로부터 effective address를 읽기

▽ instuction을 실행

참고로 세번째 단계는 명령어의 종류에 따라 스킵할 수도 안할 수도 있는데, 잠시 뒤 설명할 것이다.

[ 명령어 수행에 대한 이해 plus ]

컴퓨터는 항상 i번째 명령어를 수행중이다. 지금 내가 글을 작성하고 있는 순간에는, 컴퓨터가 i번째 명령어를 fetch하거나, decode중이거나, 유효주소를 읽는 중이거나, instruction을 수행 중이거나 넷중 하나의 과정을 거치고 있다. 그리고 i+1명령어를 수행하고.. 반복! 컴퓨터가 하는 일은 이것이 끝이다. 3GHz면 1초에 30억번 슈슈슉!!

fetch와 decode부분에서 일어나는 마이크로연산은 다음과 같았다.

time T0, T1에서 fetch가 일어나고,

time T2에서 decode가 일어났다.

T0 : AR <- PC

T1 : IR <- M[AR],

PC <- PC + 1

T2 : D0, ..., D7 <- decode IR(12-14),

AR <- IR(0-11),

I <- IR(15)

이렇게 Fetch와 Decode하는 데에 총 3클락이 소요되었다.

그럼 그 다음 과정인

▽ 메모리로부터 effective address를 읽기

▽ instuction을 실행

이 단계는 어떻게 이루어질까? 나중에 다 확인할 것이다.

일단 Fetch부터 차근차근 확인해보자.

instruction cycle - Fetch (T0, T1)

아래 회로는 istruction cycle에서 T0, T1에서 일어나는 Fetch과정을 보기 위한 회로다.

time T0, T1이 켜지면 이루어지는 일들을 확인해볼 것이다.

왼쪽 그림: time T0가 켜질 때의 상황

오른쪽 그림: time T1이 켜질 때의 상황

왼쪽 그림은 빨/파/연두 순서로 보면 되고 | 오른쪽 그림은 빨/파 순서로 보면 된다.

왼쪽 그림: time T0가 켜지면,

- selection signal S2S1S0는 010이 되어 출력 2에 연결된 레지스터의 데이터가 BUS에 실린다. 잘 보면 PC의 값이 BUS에 실렸고, PC가 bus master가 되었다. 한편, T0가 켜졌기 때문에 AR레지스터에 연결된 control signal인 LD(로드)가 enable된 모습이다.

- 이렇게 T0가 켜진 상황에서 이제 파란색 Clock 신호가 켜져서 LD를 수행하게 된다. 즉 BUS에 실렸던 값인 값을 AR레지스터로 로드하게 된다. 즉, T0 : AR <- PC의 동작을 하게 된 것이다! 그리고 AR에 저장된 그 Address값은 Memory에 올라간다.

오른쪽 그림: time T1이 켜지면,

- selection signal S2S1S0는 111이 되어 출력 7에 연결된 레지스터의 데이터가 BUS에 실린다. 잘 보면 Memory unit의 값이 BUS에 실리는데, 이전에 T0에서 Address를 Memory에 넣었었다. 즉, BUS에 Address 값이 실린다. 한편, T1이 켜졌기 때문에 Memory unit의 Read 신호가 켜졌고(enable), IR레지스터의 LD신호가 켜졌고(enable), PC레지스터의 INR신호가 켜졌다(enable).

- 이렇게 T1가 켜진 상황에서 이제 파란색 Clock 신호가 켜져서, IR레지스터의 LD신호가 수행되어 BUS에 실려있는 값이 IR레지스터로 들어온다(T1 : IR <- M[AR]). 그리고 PC레지스에 연결된 INR신호도 수행되어 PC값을 increment하게된다(T1 : PC <- PC+1)

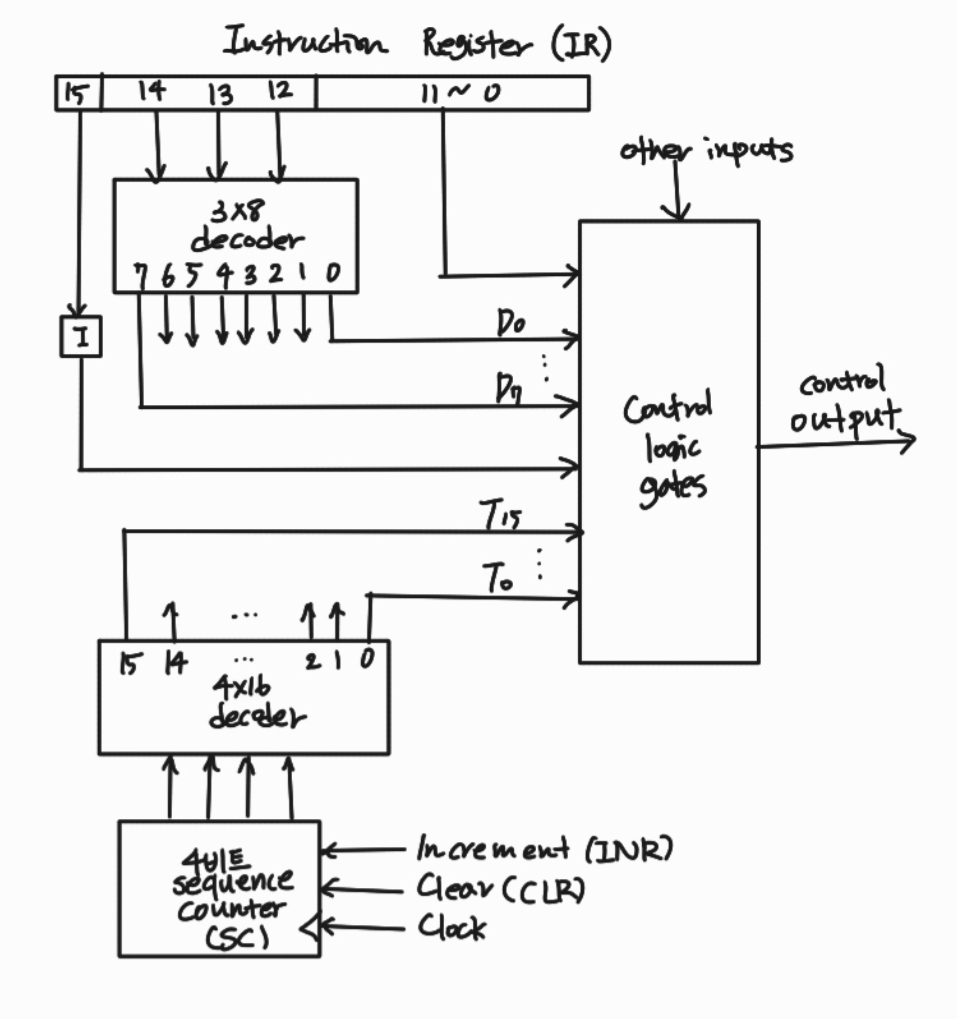

instruction cycle - 디코드 (T2)

이 부분은 지난 포스팅에서 회로로 확인했다.

IR의 각 비트들이 적절한 레지스터에 담기는 모습을 볼 수 있다.

instruction cycle - AR에 주소 담기, 그리고 실행! (T3)

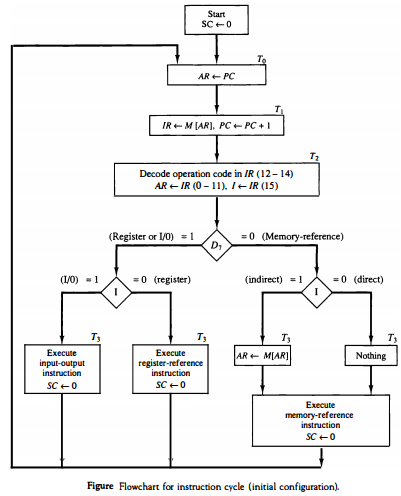

여기서 다시보는 insturction 사이클!

▽ 메모리로부터 instruction을 fetch (T0, T1)

▽ instruction을 decode (T2)

▽ 메모리로부터 effective address를 읽기 (instruction 타입에 따라 다르다!)

▽ instuction을 실행

이제 T3에서 일어날 '메모리로부터 effective address를 읽기' 부분을 확인할 것이다.

그런데 이 T3는 명령어의 타입에 따라 스킵될 수도, 수행될 수도 있다.

명령어의 타입이라고?

instruction은 최상위비트 네개가 어떤지에 따라 세가지로 나눌 수 있다고 했다.

(기억 안나면 포스팅 참고: [컴퓨터구조] 16비트 컴퓨터를 설계하자 - Instruction set 정의하기)

■ memory-reference instruction : 최상위비트 하나가 addressing mode고,

그 다음 비트 세개가 operation을 결정하는 명령코드 (피연산자가 필요)

■ register-reference : 최상위비트 네개가 0 1 1 1 이다. (피연산자 필요없음)

■ input-output instruction : 최상위비트 네개가 1 1 1 1 이다. (피연산자 필요없음)

- memery-reference 명령어는 피연산자가 존재하여 피연산자의 주소정보가 필요하기에 ▽ 메모리로부터 effective address를 읽기라는 단계를 밟을 필요가 있지만,

- register-reference 명령어나 input-output 명령어는 피연산자가 애초에 필요 없는 명령이라 그런 주소 자체가 필요 없기 때문에, ▽ 메모리로부터 effective address를 읽기단계를 밟을 필요가 전혀 없다. 그래서 이 경우에는 T3에 ▽ instuction을 실행하게 된다.

그래서 명령어의 타입을 판단할 필요가 있는 것이다!

일단 IR에 fetch된 명령어가 T2에서 decode되고 나서 D0~D7이 만들어졌던 것을 회상하자.

(기억이 잘 안나면 더보기 클릭!)

그 D0~D7의 8가지 신호는 명령어코드의 15~0비트중에 14,13,12자리에 있던 비트가 만들어내는 값이었다. 이 값으로 명령어의 타입을 알아낼 수 있다는 얘기다! 타입을 알아내서 ▽ 메모리로부터 effective address를 읽기를 수행할지 말지 판단해야 하니까.

일단 그걸 판단하는 과정은 아래 회로에 포함되어있다.

이 회로에서 보여주는 것은 fetch, decode 후에 effective address를 읽거나 읽지 않고 최종적으로 execute해내는 과정이다. 즉, instruction cycle의 흐름 정리라고 할 수 있다.

회로에서 fetch, decode가 수행된 뒤를 보면 D7가 1이냐 0이냐를 판단하고 있다.

D7가 1: 세비트(14,13,12)가 111이다. => 피연산자의 주소를 다룰 필요가 없는 명령어기 때문에 AR<-M[AR] 과정은 스킵한다. 따라서 T3에 execute한다. (플립플롭(레지스터) I에 넣어뒀던 최상위비트값으로 io명령어인지 register-ref명령어인지 판단하긴 한다.)

D7가 0: 세비트(14,13,12)가 111이 아니다. 즉, 000~011이다. => memory-reference insturction이라서 만약 indirect모드일 경우 AR<-M[AR] 과정을 거쳐야 한다! (direct모드면 아무 mirco연산도 일어나지 않아서 T3는 그냥 쉬어가는 클락이 된다.)T3에 AR<-M[AR]하고 T4에 execute한다.

(참고: indirect모드면 T3에 AR에 최종적으로 값이 담기고, direct모드면 T2에 decoding할 때 AR에 최종적으로 값이 담긴다. )

그리고 마지막으로 Sequence Counter를 0으로 초기화하여 time T0로 만들고 다시 다음 명령어에 대한 사이클을 돈다. 자 이렇게 명령사이클을 확인했다!

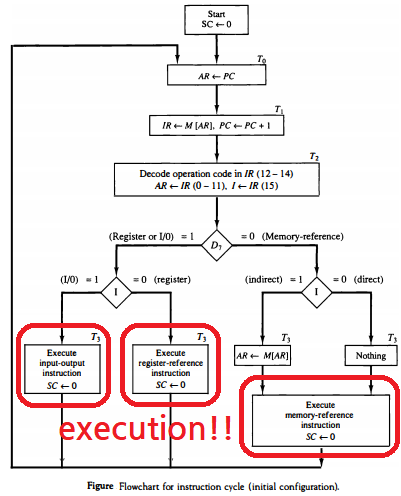

instruction cycle - 실행 (T3 or T4)

방금 보고 온 아래 회로의 execution 부분에선 어떤 micro-operation이 일어나는지 확인해볼 차례다.

이 execution 단계에서는 어떤 micro-operation이 이루어지는지는 명령어의 종류별로 좀 다른데,

다음 포스팅에서 설명할 것이다.

이번 포스팅에서 본 것은?

■ Instruction Cycle을 확인했다.

■ Instruction Cycle의 fetch, decode, effective address, execute 부분을 확인했고, 특히 effective address를 메모리로 불러오는 과정을 거치는 경우와 거치지 않는 경우를 확인했다.

■ execute의 자세한 마이크로연산 과정은 명령어의 세가지 종류별로 다른데, 이건 다음 포스팅에서 확인해보자!

다음 포스팅

[컴퓨터구조] 16비트 컴퓨터 설계하기 - 명령어의 실행단계에서 벌어지는 일들

'컴퓨터구조 & OS' 카테고리의 다른 글

| [컴퓨터구조] 16비트 컴퓨터 설계하기 - I/O instruction의 실행 단계에서 벌어지는 일들 (0) | 2021.10.16 |

|---|---|

| [컴퓨터구조] 16비트 컴퓨터 설계하기 - 명령어의 실행단계에서 벌어지는 일들 (2) | 2021.10.15 |

| [컴퓨터구조] 16비트 컴퓨터 설계하기 - Control unit 설계 (0) | 2021.10.14 |

| [컴퓨터구조] 16비트 컴퓨터를 설계하자 - Instruction set 정의하기 (0) | 2021.10.13 |

| [컴퓨터구조] 16비트 컴퓨터 설계하기 - 레지스터를 정의하자 (0) | 2021.10.13 |